# **AP702**

# USB Host and PLL Interface with DSP and MCU Controller

**Data Sheet**

Revision 0.5 September 01, 2008

# **Table of Contents**

| 1.                   | OVERVIEW                             | 1      |

|----------------------|--------------------------------------|--------|

| 2.                   | APPLICATIONS                         | 1      |

| 3.                   | FEATURES                             | 1      |

| 4.                   | ORDERING INFORMATION                 | 1      |

| 5.                   | BLOCK DIAGRAM                        | 2      |

| 6.                   | PIN CONFIGURATION                    | 3      |

| 7.                   | DEVICE PIN DESCRIPTION               | 3      |

| 8.                   | EXTERNAL MEMORY CONFIGURATION        | 6      |

| 8.1<br>8.2           |                                      |        |

| 9.                   | ELECTRICAL SPECIFICATION             | 6      |

| 9.1<br>9.2<br>9.3    | 2 RECOMMENDED OPERATING CONDITION    | 6      |

| 10.                  | PACKAGE INFORMATION                  | 6      |

| 11.                  | SOLDERING INDICATION                 | 6      |

| 1.<br>2.<br>3.<br>4. | Wave Soldering                       | 6<br>6 |

| Fig                  | gures                                |        |

| Figur                | RE 1. BLOCK DIAGRAM OF AP702         | 2      |

| Figur                | RE 2. 128 PIN LQFP PACKAGE OF AP702  | 3      |

| Figur                | RE 3. LQFP PACKAGE DIMENSION DRAWING | 6      |

#### OVERVIEW

AP702 is an USB Host and PLL Interface with DSP and MCU Controller. It has a built-in 24-bit DSP for MP3 and WMA decoding, an 8-bit MCU for CD servo control, ISO9660 file system handling and user interface function control. An USB host controller is included in AP702 to support the data control and playback of MP3 files on portable MP3 players. AP702 also offers SD card support, giving the end customers a luxury of a SD card plug-and-play element. This chip also has an on-chip PLL controller for external tuner IC to form a complete digital tuning system. This system-on-chip solution is ideal for CD-base audio products

#### 2. APPLICATIONS

- · Micro or mini stereo sound system

- · iPod docking system

- Boom box

#### 3. FEATURES

#### **CD Servo Interface and Control**

- Interface to external CD servo controller

- Built-in CD ROM C3 ECC and EDC error detection and correction

#### **MP2 Decoding**

- Support 11.025/32/48/44.1/48kHz sampling frequencies and bit rate from 32kbps to 320kbps

- Support mono and stereo audio playback

- Support 22.05/24KHz sampling frequencies and bit rate from 8kbps to 160kbps

#### **MP3 Decoding**

- Support 16/22.05/24/32/44.1/48kHz sampling frequencies and bit rate from 32kbps to 320kbps

- Support single channel, dual channel, stereo, and joint stereo audio playback

- · Support any combination of intensity stereo and MS stereo

- Support MP3 ID3 version up to version 2.4

#### **MP3 Encoding**

- Support 44.1kHz sampling frequency and bit rate from 64kbps to 128kbps

- Support stereo audio encoding

- 1x encode speed

#### **WMA Decoding**

- Support 32/44.1/48kHz sampling frequencies and bit rates of 64kbps to 320kbps

- Support single channel, dual channel, stereo, and joint stereo audio playback

#### **USB Host and SD Card Support**

- Support direct connection of USB mass storage class device into the system, such as portable MP3 player and USB flash drive

- USB card reader support

- Normal, Mini Micro SD Card support

- SDHC SD Card support

- Support FAT 12, 16 and 32 file system

#### 4. ORDERING INFORMATION

| Ordering Number | Pins | Package |

|-----------------|------|---------|

| AP702-LQ-L      | 128  | LQFP    |

Revision 0.5 Page 1 of 11 September 01, 2008

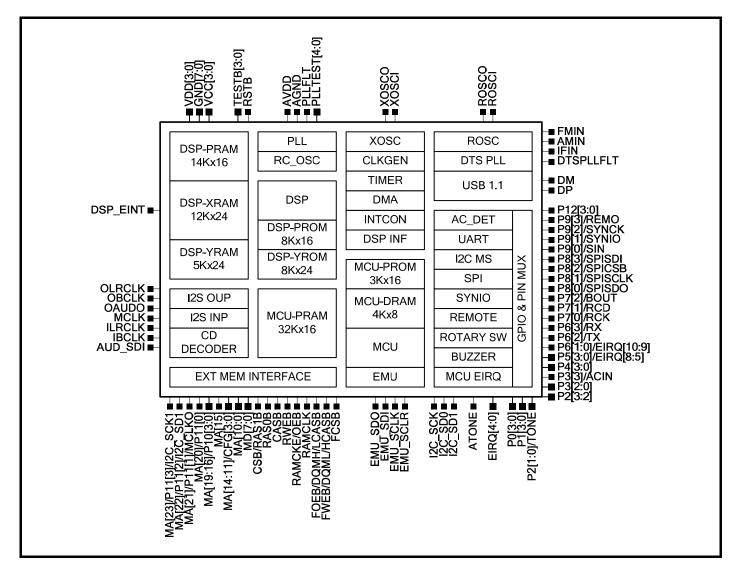

#### 5. BLOCK DIAGRAM

Figure 1. Block Diagram of AP702

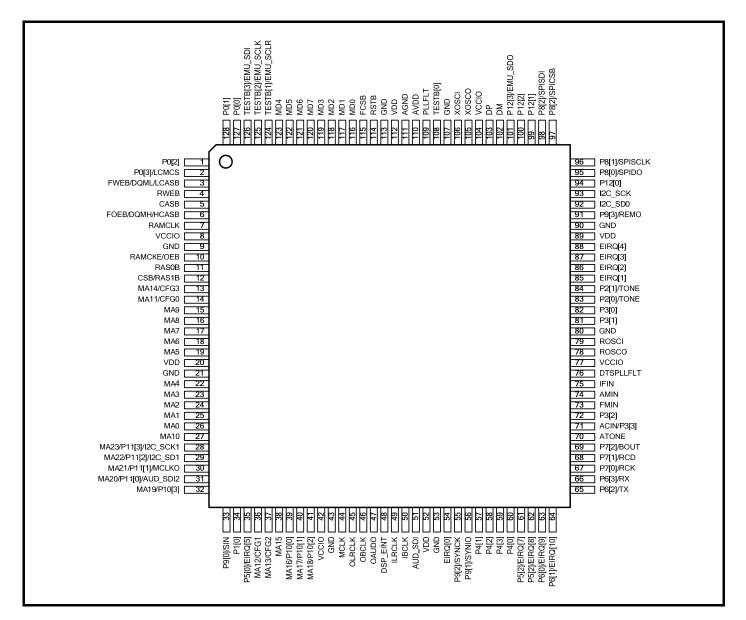

#### 6. PIN CONFIGURATION

Figure 2. 128 Pin LQFP Package of AP702

#### 7. DEVICE PIN DESCRIPTION

| Pin No. | Name            | Type | Drive (mA) | Descriptions                                              |

|---------|-----------------|------|------------|-----------------------------------------------------------|

| 1       | P0[2]           | 10   | 4          | General purpose IO port                                   |

| 2       | P0[3]/LCMCS     | 10   | 4          | General purpose IO port or LCM chip select                |

| 3       | FWEB/DQML/LCASB | 0    | 8          | WEB for NOR-Flash     DQML for SDRAM     CASB for EDO     |

| 4       | RWEB            | 0    | 8          | WEB for SDRAM or EDO     WEB for NOR Flash                |

| 5       | CASB            | 0    | 8          | CASB for SDRAM                                            |

| 6       | FOEB/DQHM/HCASB | 0    | 8          | OEB for NOR-Flash   DQMH for SDRAM   HCASB for 16-bit EDO |

# USB Host and PLL Interface with DSP and MCU Controller

| Pin No.  | Name                       | Туре     | Drive (mA)    | Descriptions                                                                                   |

|----------|----------------------------|----------|---------------|------------------------------------------------------------------------------------------------|

| 7        | RAMCLK                     | 0        | 8             | SDRAM operating clock                                                                          |

| 8        | VCCIO                      | -        | -             | 3.3V IO power supply                                                                           |

| 9        | GND                        | -        | -             | Ground                                                                                         |

| 10       | RAMCKE/OEB                 | 0        | 8             | 1. CKE for SDRAM                                                                               |

|          |                            |          |               | 2. OEB for EDO                                                                                 |

| 11       | RAS0B                      | 0        | 8             | RASB for SDRAM or EDO  1. CSB for SDRAM                                                        |

| 12       | CSB/RAS1B                  | 0        | 8             | 2. RASB for 2 <sup>nd</sup> EDO device                                                         |

| 13       | MA14/CFG3                  | 0        | 8             | Memory address and reset options control bits                                                  |

| 14       | MA11/CFG0                  | 0        | 8             | Memory address and reset options control bits                                                  |

| 15       | MA9                        | 0        | 8             | Memory address                                                                                 |

| 16       | MA8                        | 0        | 8             | Memory address                                                                                 |

| 17       | MA7                        | 0        | 8             | Memory address                                                                                 |

| 18       | MA6                        | 0        | 8             | Memory address                                                                                 |

| 19       | MA5                        | 0        | 8             | Memory address                                                                                 |

| 20       | VDD                        |          |               | 1.8V core supply                                                                               |

| 21       | GND                        |          |               | Ground                                                                                         |

| 22       | MA4                        | 0        | 8             | Memory address                                                                                 |

| 23<br>24 | MA3<br>MA2                 | 0        | <u>8</u><br>8 | Memory address                                                                                 |

| 25       | MA1                        | 0        | 8             | Memory address Memory address                                                                  |

| 26       | MA0                        | 0        | 8             | Memory address                                                                                 |

| 27       | MA10                       | 0        | 8             | Memory address                                                                                 |

|          | 1411/4110                  |          | - J           | Memory address                                                                                 |

| 28       | MA23/P11[3]/I2C_SCK1       | IO       | 8             | 2. General IO port pin                                                                         |

|          | ., _                       |          |               | 3. I2C clock output                                                                            |

|          |                            |          |               | Memory address                                                                                 |

| 29       | MA22/P11[2]/I2C_SD1        | Ю        | 8             | 2. General IO port pin                                                                         |

|          |                            |          |               | 3. I2C clock output                                                                            |

| 20       | MA 04 /D44[4]/MOLICO       | 10       | 0             | 1. Memory address                                                                              |

| 30       | MA21/P11[1]/MCLKO          | Ю        | 8             | General IO port pin     16.9344MHz clock output                                                |

|          |                            |          |               | Memory address or general IO port pin or external ADC audio                                    |

| 31       | MA20/P11[0]/AUD_SDI2       | Ю        | 8             | data input                                                                                     |

| 32       | MA19/P10[3]                | Ю        | 8             | Memory address or general IO port pin                                                          |

| 33       | P9[0]/SIN                  | IO       | 4             | General IO port pin or synchronous interface data input                                        |

| 34       | P1[0]                      | 10       | 4             | General purpose IO port                                                                        |

| 35       | P5[0]/EIRQ[5]              | 10       | 4             | General purpose IO port or MCU external interrupt input                                        |

| 36       | MA12/CFG1                  | 0        | 8             | Memory address and reset options control bits                                                  |

| 37       | MA13/CFG2                  | 0        | 8             | Memory address and reset options control bits                                                  |

| 38       | MA15                       | 0        | 8             | Memory address                                                                                 |

| 39       | MA16/P10[0]                | 10       | 8             | General purpose IO port or memory address.                                                     |

| 40<br>41 | MA17/P10[1]<br>MA18/P10[2] | 10<br>10 | 8<br>8        | General purpose IO port or memory address.                                                     |

| 42       | VCCIO                      | 10       | 0             | General purpose IO port or memory address.  3.3V IO power supply                               |

| 43       | GND                        |          |               | Ground                                                                                         |

| 44       | MCLK                       | IO       | 4             | 16.9344MHz output clock to external DAC or ADC                                                 |

| 45       | OLRCLK                     | IO       | 4             | Sampling clock for external DAC or ADC                                                         |

| 46       | OBCLK                      | IO       | 4             | Bit clock for external DAC or ADC                                                              |

| 47       | OAUDO                      | Ю        | 4             | Serial data for external DAC or ADC                                                            |

| 48       | DSP_EINT                   | 1        | -             | DSP external interrupt input                                                                   |

| 49       | ILRCLK                     | 1        | -             | Sampling clock input                                                                           |

| 50       | IBCLK                      | <u> </u> | -             | Bit clock input                                                                                |

| 51       | AUD_SDI                    | <u> </u> | -             | Audio data input                                                                               |

| 52       | VDD                        |          |               | 1.8V core supply                                                                               |

| 53       | GND                        |          |               | Ground MCU external interrupt input pin                                                        |

| 54       | EIRQ[0]                    | I        | -             | MCU external interrupt input pin General purpose IO port or synchronous serial interface clock |

| 55       | P9[2]/SYNCK                | Ю        | 4             | output                                                                                         |

| 56       | P9[1]/SYNIO                | Ю        | 4             | General purpose IO port or synchronous serial interface bidirectional data                     |

| 57       | P4[1]                      | Ю        | 4             | General purpose IO port                                                                        |

| 58       | P4[2]                      | Ю        | 4             | General purpose IO port                                                                        |

| 59       | P4[3]                      | Ю        | 4             | General purpose IO port                                                                        |

| 60       | P4[0]                      | IO       | 4             | General purpose IO port                                                                        |

| 61       | P5[2]/EIRQ[7]              | 10       | 4             | General purpose IO port or MCU external interrupt input                                        |

| 62       | P5[3]/EIRQ[8]              | 10       | 4             | General purpose IO port or MCU external interrupt input                                        |

| 63       | P6[0]/EIRQ[9]              | 10       | 4             | General purpose IO port or MCU external interrupt input                                        |

| 64       | P6[1]/EIRQ[10]             | Ю        | 4             | General purpose IO port or MCU external interrupt input                                        |

# **AP702**

# USB Host and PLL Interface with DSP and MCU Controller

| Pin No.    | Name              | Туре     | Drive (mA) | Descriptions                                                |

|------------|-------------------|----------|------------|-------------------------------------------------------------|

| 65         | P6[2]/TX          | 10       | 4          | General purpose IO port or UART TX output                   |

| 66         | P6[3]/RX          | 10       | 4          | General purpose IO port pin or UART RX input                |

| 67         | P7[0]/RCK         | 10       | 4          | General purpose IO port pin or rotary switch counter input  |

| 68         | P7[1]/RCD         | 10       | 4          | General purpose IO port pin or rotary switch counter input  |

| 69         | P7[2]/BOUT        | 10       | 4          | General purpose IO port pin or UART clock output            |

| 70         | ATONE             | Α        | -          | Buzzer output with level control                            |

| 71         | P3[3]/ACIN        | 10       | 4          | General purpose IO port pin or 50/60Hz AC detection input   |

| 72         | P3[2]             | 10       | 4          | General purpose IO port pin                                 |

| 73         | FMIN              |          | -          | FM input clock                                              |

| 74         | AMIN              | l        | -          | AM input clock                                              |

| 75         | IFIN              |          | -          | IF input clock                                              |

| 76         | DTSPLLFLT         | 10       | 4          | DTS PLL control voltage output                              |

| 77         | VCCIO             |          |            | 3.3V IO power supply                                        |

| 78         | ROSCO             | 0        | -          | 75kHz oscillator output                                     |

| 79         | ROSCI             |          | -          | 75kHz oscillator input                                      |

| 80         | GND               |          |            | Ground                                                      |

| 81         | P3[1]             | 10       | 4          | General purpose IO port pin                                 |

| 82         | P3[0]             | 10       | 4          | General purpose IO port pin                                 |

| 83         | P2[0]/TONE        | 10       | 4          | General purpose IO port pin or buzzer output                |

| 84         | P2[1]/TONE        | IO       | 4          | General purpose IO port pin or buzzer output                |

| 85         | EIRQ[1]           | <u> </u> | -          | MCU external interrupt input pin                            |

| 86         | EIRQ[2]           | <u> </u> | -          | MCU external interrupt input pin                            |

| 87         | EIRQ[3]           | <u> </u> | -          | MCU external interrupt input pin                            |

| 88         | EIRQ[4]           |          | -          | MCU external interrupt input pin                            |

| 89         | VDD               |          |            | 1.8V core supply                                            |

| 90         | GND               |          |            | Ground                                                      |

| 91         | P9[3]/REMO        | 10       | 4          | General purpose IO port pin or remote receiver input        |

| 92         | I2C_SD0           | 10       | 4          | I2C bus data                                                |

| 93         | I2C_SCK           | 10       | 4          | I2C bus clock                                               |

| 94         | P12[0]            | 10       | 4          | General purpose IO port pin                                 |

| 95         | P8[0]/SPIDO       | 10       | 4          | General purpose IO port pin or SPI data output              |

| 96         | P8[1]/SPISCLK     | 10       | 4          | General purpose IO port pin or SPI clock                    |

| 97         | P8[2]/SPICSB      | 10       | 4          | General purpose IO port pin or SPI chip select              |

| 98         | P8[3]/SPISDI      | 10       | 4          | General purpose IO port pin or SPI data input               |

| 99         | P12[1]<br>P12[2]  | 10       | 4          | General purpose IO port pin                                 |

| 100        |                   | 10       | 4          | General purpose IO port pin                                 |

| 101        | P12[3]/EMU_SDO    | 10       | 4          | General purpose IO port pin or emulator data output         |

| 102        | DM                | 10       |            | USB transceiver negative data pin                           |

| 103        | DP                | Ю        |            | USB transceiver positive data pin                           |

| 104        | VCCIO             |          |            | 3.3V IO power supply                                        |

| 105<br>106 | XOSCO<br>XOSCI    | 0        |            | 16.9344MHz oscillator output<br>16.9344MHz oscillator input |

| 106        | GND               | l        |            | Ground                                                      |

| 107        |                   |          |            | Active low chip test enable                                 |

|            | TESTB[0]          | <u>Ι</u> | -          |                                                             |

| 109<br>110 | PLLFLT<br>AVDD    | Α        | -          | PLL filter  1.8V supply for PLL                             |

| 111        | AGND              |          |            | Analog ground for PLL                                       |

| 112        | VDD               |          |            | 1.8V core supply                                            |

| 113        | GND               |          |            | Ground                                                      |

| 114        | RSTB              | 1        | _          | Active low chip reset input                                 |

| 115        | FCSB              | 0        | 8          | Flash chip select                                           |

| 116        | MD0               | 10       | 8          | Memory data bus                                             |

| 117        | MD1               | 10<br>10 | 8          | Memory data bus                                             |

| 118        | MD2               | 10<br>10 | 8          | Memory data bus                                             |

| 119        | MD3               | 10<br>10 | 8          | Memory data bus                                             |

| 120        | MD7               | 10<br>10 | 8          | Memory data bus                                             |

| 121        | MD6               | 10<br>10 | 8          | Memory data bus                                             |

| 121        | MD5               | 10<br>10 | 8          | Memory data bus                                             |

| 123        | MD4               | 10       | 8          | Memory data bus                                             |

| 124        | TESTB[1]/EMU_SCLR | <u></u>  | -          | Active low chip test enable or emulator reset input         |

| 125        | TESTB[2]/EMU_SCLK | <u> </u> | _          | Active low chip test enable or emulator data clock input    |

| 126        | TESTB[3]/EMU_SDI  | <u> </u> | _          | Active low chip test enable or emulator serial data input   |

| 127        | P0[0]             | IO       | 4          | General purpose IO port                                     |

| 128        | P0[1]             | 10       | 4          | General purpose IO port                                     |

| 140        | · •[·]            | 10       | т т        | Control purpose to port                                     |

#### 8. EXTERNAL MEMORY CONFIGURATION

## **8.1** Supporting Memory Devices

| Memory Device |        | Configurations | Configurations |                |  |

|---------------|--------|----------------|----------------|----------------|--|

| Memory Device | 4 bits | 8 bits         | 16 bits        | support device |  |

|               |        | 64k x 8        |                |                |  |

|               |        | 128k x 8       |                |                |  |

| NOR Flash     | -      | 256k x 8       | -              | 1              |  |

|               |        | 512k x 8       |                |                |  |

|               |        | 1M x 8         |                |                |  |

|               |        | 2M x 8         | 1M x 16        |                |  |

| SDRAM         | -      | 8M x 8         | 4M x 16        | 1              |  |

| SDRAW         |        | 16M x 8        | 8M x 16        | l l            |  |

|               |        | 32M x 8        | 16M x 16       |                |  |

| EDO           | 1M x 4 | 512k x 8       |                | 2              |  |

| EDO           | 4M x 4 | 2M x 8         | _              | 2              |  |

## **8.2 External Memory Connection**

| OFD400 Pin No  | Din Nama        | Data RAM  |                 | NOD Floor | 1.014 |

|----------------|-----------------|-----------|-----------------|-----------|-------|

| QFP128 Pin No. | Pin Name        | SDRAM     | EDO             | NOR Flash | LCM   |

| 115            | FCSB            |           |                 | CS#       |       |

| 116            | MD[0]           | D0/D8     | D0              | D0        | D0    |

| 117            | MD[1]           | D1/D9     | D1              | D1        | D1    |

| 118            | MD[2]           | D2/D10    | D2              | D2        | D2    |

| 119            | MD[3]           | D3/D11    | D3              | D3        | D3    |

| 120            | MD[7]           | D7/D15    | D7              | D7        | D7    |

| 121            | MD[6]           | D6/D14    | D6              | D6        | D6    |

| 122            | MD[5]           | D5/D13    | D5              | D5        | D5    |

| 123            | MD[4]           | D4/D12    | D4              | D4        | D4    |

| 2              | P0[3]/LCMCS     |           |                 |           | CS    |

| 3              | FWEB/DQML/LCASB | DQML      | CAS#            | WE#       |       |

| 4              | RWEB            | WE#       |                 |           |       |

| 5              | CASB            | CAS#      |                 |           |       |

| 6              | FOEB/DQHM/HCASB | DQMH      | CAS#            | OE#       |       |

| 7              | RAMCLK          | CLK       |                 |           |       |

| 10             | RAMCKE/OEB      | CKE       | OE#             |           |       |

| 11             | RAS0B           | RAS#      | RAS# (device 1) |           |       |

| 12             | CSB/RAS1B       | CS#       | RAS# (device 2) |           |       |

| 13             | MA14/CFG3       |           |                 | A14       |       |

| 14             | MA11/CFG0       | A11       |                 | A11       |       |

| 15             | MA9             | A9        | A9              | A9        |       |

| 16             | MA8             | A8        | A8              | A8        |       |

| 17             | MA7             | A7        | A7              | A7        |       |

| 18             | MA6             | A6        | A6              | A6        |       |

| 19             | MA5             | A5        | A5              | A5        |       |

| 22             | MA4             | A4        | A4              | A4        |       |

| 23             | MA3             | A3        | A3              | A3        |       |

| 24             | MA2             | A2        | A2              | A2        |       |

| 25             | MA1             | A1        | A1              | A1        |       |

| 26             | MA0             | A0        | A0              | A0        | A0    |

| 27             | MA10            | A10       | A10             | A10       |       |

| 36             | MA12/CFG1       | A12 (BA1) |                 | A12       |       |

| 37             | MA13/CFG2       | A13 (BA0) |                 | A13       |       |

| 38             | MA15            |           |                 | A15       |       |

| 39             | MA16/P10[0]     |           |                 | A16       |       |

| 40             | MA17/P10[1]     |           |                 | A17       |       |

| 41             | MA18/P10[2]     |           |                 | A18       |       |

#### 9. ELECTRICAL SPECIFICATION

#### 9.1 Absolute Maximum Ratings

Under no circumstances the absolute maximum ratings given below should be violated.

Caution: exceeding one or more of the limiting values may cause permanent damage to the device.

| Parameter                                     | Symbol           | Rating       | Unit |

|-----------------------------------------------|------------------|--------------|------|

| Power Supply Voltage (IO)                     | VCCIO            | -0.3 to 4.0  | V    |

| Power Supply Voltage (Core)                   | VDD              | -0.3 to 2.16 | V    |

| Power Supply Voltage (analog)                 | AVDD             | -0.3 to 2.16 | V    |

| Input Voltage                                 | V <sub>IN</sub>  | -0.3 to 4.0  | V    |

| Power Dissipation (Ta = 70°C)                 | P <sub>d</sub>   | TBD          | mW   |

| Storage Temperature                           | T <sub>STG</sub> | -40 to 150   | °C   |

| DC input current for each I/O pin             | I <sub>IN</sub>  | 20           | mA   |

| Output short circuit current for each I/O pin | l <sub>оит</sub> | 20           | mA   |

#### 9.2 Recommended Operating Condition

| Parameter                         | Symbol           | Min. | Тур. | Max.  | Unit |

|-----------------------------------|------------------|------|------|-------|------|

| Power Supply Voltage (IO)         | VCCIO            | 3.0  | 3.3  | 3.6   | V    |

| Power Supply Voltage (Core Logic) | VDD              | 1.62 | 1.8  | 1.98  | V    |

| Power Supply Voltage (Analog)     | AVDD             | 1.62 | 1.8  | 1.98  | V    |

| Input Voltage (Digital)           | V <sub>IN</sub>  | 0    | -    | VCCIO | V    |

| Input Voltage (Analog)            | V <sub>IN</sub>  | 0    | -    | AVDD  | V    |

| Operating Temperature             | T <sub>OPR</sub> | -20  | ·=   | +85   | °C   |

#### 9.3 Electrical Characteristics

(VCCIO=3.3V±10%, VDD=1.8V±10%, AVDD=1.8V±10%, Operating temperature = 0°C - 70°C)

| Symbol                       | Parameter                              | Condition                                      | Min. | Тур. | Max. | Unit |

|------------------------------|----------------------------------------|------------------------------------------------|------|------|------|------|

| V <sub>IH</sub>              | Input High Voltage                     |                                                | 2.0  | -    | -    | V    |

| $V_{IL}$                     | Input Low Voltage                      |                                                | -    | -    | 0.8  | V    |

| $R_{PU}$                     | Pull-Up Resistance                     | V <sub>IN</sub> = 0V, VCCIO = 3.3V             | 10   | 12   | 18   | kΩ   |

| $V_{ina}$                    | FMIN,AMIN,IFIN Input Voltage           |                                                | 150  |      |      | mVpp |

| I <sub>OL</sub> <sup>1</sup> | Low Level Output Current for 4mA Pins  | V <sub>OL</sub> = 0.4V<br>VCCIO = 3.3V         |      | 4    | -    | mA   |

| I <sub>OL</sub> <sup>2</sup> | Low Level Output Current for 8mA Pins  | V <sub>OL</sub> = 0.4V<br>VCCIO = 3.3V         |      | 8    | -    | mA   |

| I <sub>OH</sub>              | High Level Output Current for 4mA Pins | V <sub>OH</sub> = VCCIO - 0.4V<br>VCCIO = 3.3V |      | 4    | -    | mA   |

| I <sub>OH</sub> <sup>2</sup> | High Level Output Current for 8mA Pins | V <sub>OH</sub> = VCCIO - 0.4V<br>VCCIO = 3.3V |      | 8    | -    | mA   |

| ldd_opr                      | Core operating Current Idd @ VDD       | Full Functional Mode, DSP<br>Run at 96 MHz     | -    | 30   | -    | mA   |

| ldd_idle                     | Power Down Current<br>Idd @ VDD        | STOP Mode<br>VCCIO = 3.6V<br>VDD = 1.98V       | -    | 300  | 800  | μA   |

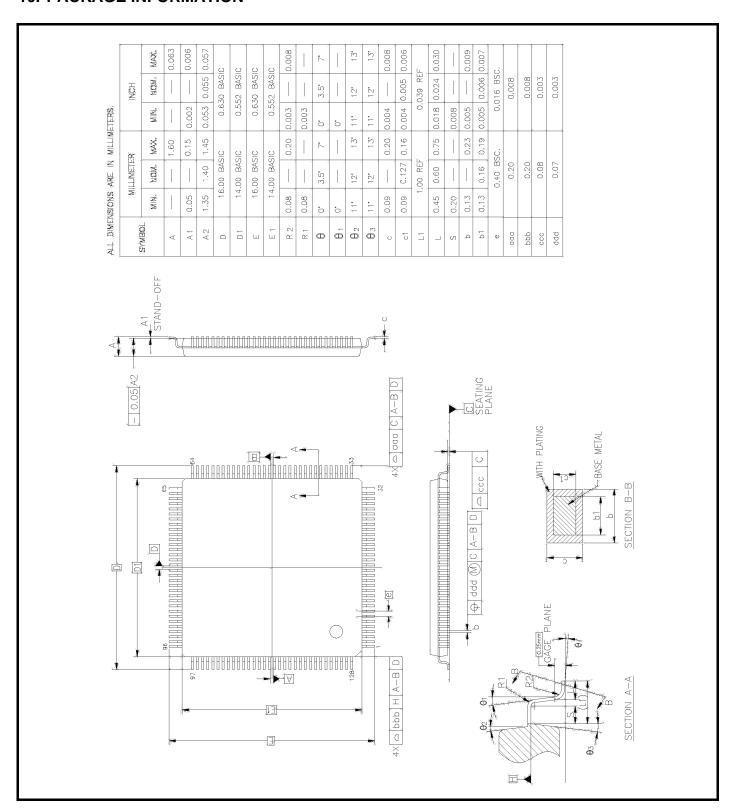

#### 10. PACKAGE INFORMATION

Figure 3. LQFP Package Dimension Drawing

# USB Host and PLL Interface with DSP and MCU Controller

#### 11. SOLDERING INDICATION

This section gives a very brief insight to a complex technology. There is no soldering method that is ideal for all surface mount IC packages. Wave soldering can still be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In these situations reflow soldering is recommended.

#### 1. Reflow Soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stenciling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 220 °C for thick/large packages, and below 235 °C for small/thin packages.

#### 2. Wave Soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used, the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch:

- larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### 3. Manual Soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

Revision 0.5 Page 9 of 11 September 01, 2008

#### 4. Suitability of Surface Mount IC Packages for Wave and Reflow Soldering Methods

| Package                                             | Soldering Method       |            |  |

|-----------------------------------------------------|------------------------|------------|--|

| rackaye                                             | Wave                   | Reflow (1) |  |

| BGA, HBGA, LFBGA, SQFP, TFBGA                       | Not suitable (2)       | Suitable   |  |

| HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, HVQFN, SMS | Not suitable           | Suitable   |  |

| PLCC (3), SO, SOJ                                   | Suitable               | Suitable   |  |

| LQFP, QFP, TQFP                                     | Not recommended (3)(4) | Suitable   |  |

| SSOP, TSSOP, VSO                                    | Not recommended (5)    | Suitable   |  |

#### **Notes**

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect).

- 2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

- 3. If wave soldering is considered, the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch equal to or smaller than 0.5 mm.

Revision 0.5 Page 10 of 11 September 01, 2008

Valence Semiconductor Design Limited Unit 2001, 20/F, APEC Plaza, 49 Hoi Yuen Road, Kwun Tong, Hong Kong

Tel: (852) 2797 3288 Fax: (852) 2776 7770

Email: <u>inquiry@valencetech.com</u> Website: http://www.valencetech.com

#### IMPORTANT NOTICE

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available. ValenceTech Ltd. and its affiliates ("Valence") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied contained in this document is accurate and reliable. However, the information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by Valence for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Valence and by furnishing this information, valence grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Valence owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Valence integrated circuits or other products of Valence. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale. An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan. An export license and /or quota needs to be obtained from the competent authorities of the Chinese Government if any of the product

This product includes technology owned by Microsoft Corporation and cannot be used or further distributed without a license from Microsoft or a Microsoft affiliate.

Revision 0.5 Page 11 of 11 September 01, 2008